Silicon IP Cores

JPEG Image Compression

Encoders, Decoders, Reference Designs, and more for images & video

|

Need lossless image compression? See the Lossless Image Compression Family page for JPEG-LS, QOI, and more. |

This IP Family offers a set of efficient hardware encoders and decoders

for Lossy compression with JPEG and its application to video using Motion JPEG.

All cores are highly optimized custom hardware engines operating autonomously without software assistance. They feature high

throughput, small silicon footprint, low energy consumption, and low latency. Over 100 customers have used JPEG cores from CAST in various applications, including smartphones, wearables, medical imaging, automotive, and aerospace. The family includes:

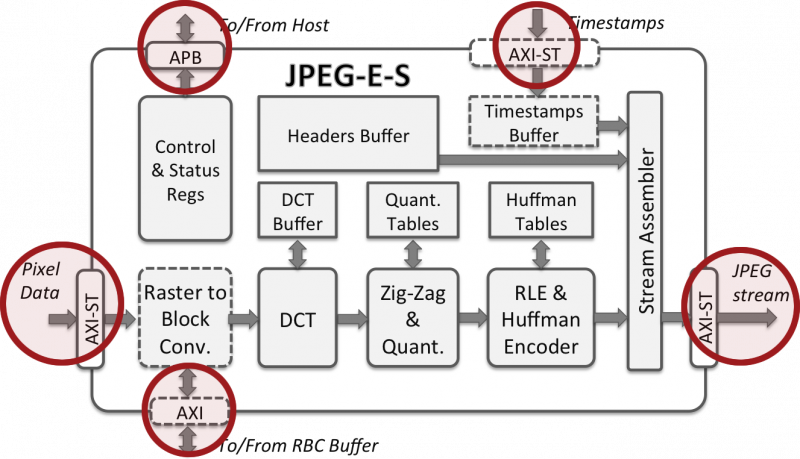

- JPEG-E-S: Baseline JPEG & Motion JPEG encoder.

- JPEG-EX-S: Baseline (8-bit) and Extended (12-bit) JPEG & Motion JPEG encoder.

- JPEG-EX-F: Baseline (8-bit) and Extended (12-bit) JPEG & Motion JPEG encoder with scalable throughput. 8K UHD capable even in low-cost FPGAs.

- JPEG-E-T: Tiny Baseline JPEG & Motion JPEG encoder, with fixed Huffman tables and no automatic bit-rate control.

- JPEG-D-S: Baseline JPEG & Motion JPEG decoder.

- JPEG-DX-S: Baseline (8-bit) and Extended (12-bit) JPEG & Motion JPEG encoder.

- JPEG-DX-F: Baseline (8-bit) and Extended (12-bit) JPEG & Motion JPEG decoder with scalable throughput. 8K UHD capable even in low-cost FPGAs.

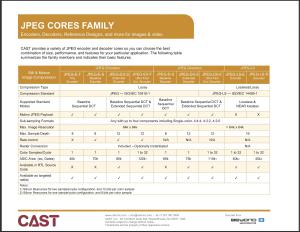

Compare the features of the JPEG cores using this table:

The family of JPEG cores is complemented by companion cores, including:

- JPEG2RTP: Hardware RTP stack for JPEG stream encapsulation, facilitates processor-less streaming.

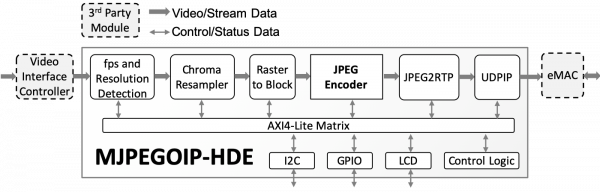

- MJPEGOIP-HDE: Low-latency Motion JPEG Over IP HD Encoder, combines compression with encapsulation.

- MM2ST: An AHB/AXI4-Lite to AXI4-Stream Bridge. enables the use of any JPEG core as a memory-mapped peripheral, with data transfers controlled by an external DMA.

- AXI4-SGDMA: An AXI4 Memory-Mapped to/from AXI4-Stream Scatter-Gather DMA. Enables the use of any JPEG core as a memory-mapped peripheral with an internal DMA.

- UDPIP-1G: Hardware UDP/IP stack enabling direct streaming over an IP network.

Great Image Compression in Lower-Cost Silicon

The small size, low power consumption, and high performance of these cores make it easy and cost-effective to add image processing to almost any product category.

Very Low Power Consumption

These dedicated hardware encoders and decoders use dramatically less power than any software or hardware/software codecs with similar capabilities.

They are all designed to use minimal silicon area, and their smaller footprint further saves energy over larger cores.

High Performance, 4K/8K Processing

Energy saving doesn’t come at the expense of processing power. The throughput of the encoders and decoders can readily scale to handle 4K, 8K, or higher frame sizes and high frame rates, even in modest FPGAs.The JPEG encoders run ultra-fast, processing up to 32 samples/cycle and easily handling up to UHD/4K video in FPGAs. Multi-channel support and multiple cores are options for the most demanding systems.

The Most Efficient High-Resolution Solutions

The Motion JPEG capabilities of the image encoders and decoders offers by far the most economical way to process up to 4K video. Yet for moderate compression levels, they provide video quality that’s practically equal to much larger and more complex H.264, H.265, or JPEG2000 encoders.

The result? These JPEG cores let you encode UHD/4K video even in smaller ASIC silicon or extremely modest FPGAs. Their scalability gets you to even higher resolutions, still with great economies.

Independent Operation

These image compression encoders and decoders operate in standalone mode. Once programmed, they function autonomously, with no need for software control or interaction with the system processor (a way for further energy savings).

Standard Interfaces

The JPEG cores use industry-standard ARM® AMBA® interfaces for easy SoC compatibility.

They use the AMBA® AXI4-Stream interface for pixel and stream data, and APB or AXI4-Lite for register access. Optional Raster Conversion further simplifies integration via an AXI interface to the lines buffer for easy connection to on- or off-chip memory. Optionally JPEG cores can be used as memory-mapped peripherals, using interface bridges with or without DMA capabilities. Check the MM2ST and AXI4-SDMA product pages, and contact us to learn more.

Efficient and Adaptable Memory Interfaces

The cores’ memory interfaces also ease integration challenges and reduce system-wide power consumption.

The JPEG cores can handle processing without accessing energy-consuming off-chip memory. It is only in the case of high-resolution video, where users may choose to use an external memory for the buffering required by the Raster Conversion functions.

To ease integration and enable the use of shared-memory resources, the Raster Conversion functions are tolerant to memory access latency, independent of memory type, and operate on a different clock than the memory device.

Evaluate JPEG cores before buying or get a head start on system development with our pre-integrated platforms for JPEG. Each combines compression cores with peripherals, interconnects, and essential software in ready-to-run FPGA board systems.

Motion-JPEG over IP Subsystems and Boards

Our off-the-shelf Motion JPEG Over IP Subsystem makes it especially easy to build in image compression over Ethernet or Wi-Fi. It includes a JPEG encoder core and everything needed to exercise it, including UDP/IP, RTP, and DMA controllers. Ready-to-run board kits are available for Altera or AMD; see the Motion JPEG Over IP product page for all the details:

MJPEGOIP-HDE Motion JPEG Video Over IP – HD Encoder Subsystem

Compare JPEG encoders and decoders in this table of specification and features.

Baseline JPEG Encoder

Baseline and Extended JPEG Encoder

Ultra-Fast Baseline and Extended JPEG Encoder

Tiny Baseline JPEG Encoder

Baseline JPEG Decoder

Baseline and Extended JPEG Decoder

Ultra-Fast Baseline and Extended JPEG Decoder

Hardware RTP Stack for JPEG Stream Encapsulation

Motion JPEG Over IP – HD Video Encoder Subsystem