Silicon IP Cores

I2C-SMBUS

I2C & SMBus Controller

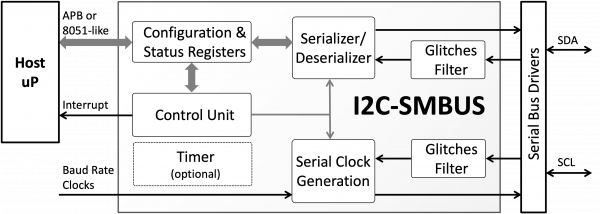

The I2C-SMBUS core implements a serial interface controller for the Inter-Integrated Circuit (I2C) bus and the System Management Bus (SMBus). The core is also suitable for implementing controllers for the Power Management Bus (PMBUS).

The core can be programmed to operate either as a bus master or a slave, and it is easy to program and integrate. An arbitration mechanism allows operation in a multiple master bus and the SMBus provisioned clock synchronization mechanism allows fast-master/slow-slave communication. Furthermore, the core detects timeout and errors to prevent bus deadlocks, and can filter out glitches on the serial line. The control, status, and data registers of the I2C-SMBUS core are accessible via an AMBA APB or a generic memory mapped interface.

The I2C-SMBUS is a microcode-free design developed for reuse in ASIC and FPGA implementations. The design uses rising-edge-triggered flip-flops only with the reset type (i.e. asynchronous and/or synchronous) being configurable at synthesis time. Furthermore, the core does not use tri-states; therefore scan insertion is straightforward.

The I2C-SMBUS can manage the communication of a host processor with peripherals such as sensors, smart battery subsystems, analog front ends, analog-to-digital and digital to analog converters, and display controllers.

The I2C-SMBUS can be mapped to any ASIC technology or FPGA device (provided sufficient silicon resources are available). The following table provides sample performance and resource utilization data. Please contact CAST to get characterization data for your target configuration and technology.

| Technology | Core Area (w/o Timer) | Timer Area | Core/Bus Clock Frequency |

|---|---|---|---|

| TSMC 90nm process | 1,650 gates | 600 gates | 100 MHz |

| TSMC 40nm process | 1,900 gates | 700 gates | 100 MHz |

I2C-SMBUS core reference designs have been evaluated in a variety of technologies. The following are sample implementation results on Altera FPGAs for the core configured with an APB interface and the optional timer instantiated.

| Family | Device | Logic | Memory Bits | Clock Freq. |

|---|---|---|---|---|

| Cyclone IV GX | EP4CGX15BF14C6 | 598 LEs | 0 | 175 MHz |

| Cyclone V | 5CEFA2F23I7 | 281 ALMs | 0 | 175 MHz |

I2C-SMBUS core reference designs have been evaluated in a variety of technologies. The following are sample implementation results on AMD FPGA for the core configured with an APB interface and the optional timer instantiated.

| Family | Device | LUTs | BRAM | Clock Freq. |

|---|---|---|---|---|

| Artix-7 | xc7a12t-1 | 593 | 0 | 100 MHz |

| Artix UltraScale+ | xcau20p-2 | 563 | 0 | 100 MHz |

| Kintex UltraScale | xcku025-2 | 566 | 0 | 100 MHz |

| Kintex UltraScale+ | xcku3p-3 | 566 | 0 | 100 MHz |

| Spartan-7 | xc7s75-1IL | 592 | 0 | 100 MHz |

| Versal Prime | xcvm1102-1LP | 492 | 0 | 100 MHz |

Support

The core as delivered is warranted against defects for ninety days from purchase. Thirty days of phone and email technical support are included, starting with the first interaction. Additional maintenance and support options are available.

Engineered by Silesia Devices.

Features List

Standards Compliance

- Phillips I2C

- SMBus Version 2.0 & 3.0

- PMBus Version 1.2 or earlier

Operation Modes

- Master Transmitter Mode

- Master Receiver Mode

- Slave Receiver Mode

- Slave Transmitter Mode

Functionality

- Seven-bit Addressing

- Byte-wide Transfers

- Bus Arbitration

- Clock signal (SCL) generation (in master mode) and data synchronization

- START/STOP Timing detection and generation

- Timeout/Bus error detection

- Clock-Low Extension to allow fast-master slow-slave communication

- Configurable glitches filter for clock and data serial lines

- Bus status reporting

Interfaces

- I2C–SMBUS

- A pair of unidirectional signals for SCL and SDA

- Control for the serial line buffers/drivers

- Host

- 32-bit APB or 8-bit generic (8051-like) for register access

- Interrupt line

- Clocks

- Core operates on the host-interface clock

- Reference clock signals used to generate the serial clock (SCL)

Deliverables

- RTL source code or targeted FPGA netlist

- Testbench

- Sample simulation and synthesis script

- Extensive documentation

- Sample SMBus software driver