Silicon IP Cores

Consider Code Density when Choosing Embedded Processors

Power consumption and area are commonly considered in choosing an embedded SoC processor, but another major factor is often overlooked in such an evaluation: the code density of the processor’s instruction set architecture (ISA).

Code Density’s Effect On Power Consumption

A denser instruction set yields smaller code, which in turn requires fewer instruction fetches. This has a major impact on efficiency, because the energy used to fetch an instruction from on-chip memory is much greater than that required for the CPU to execute that instruction.

How much greater? The 2010 Stanford dissertation study by James Balfour on Efficient Embedded Computing showed that for a typical 32-bit RISC processor, an instruction fetch from a 2 Kbyte on-chip cache consumes 6.8 times more energy than a 32-bit add operation (in a typical 45nm CMOS process).

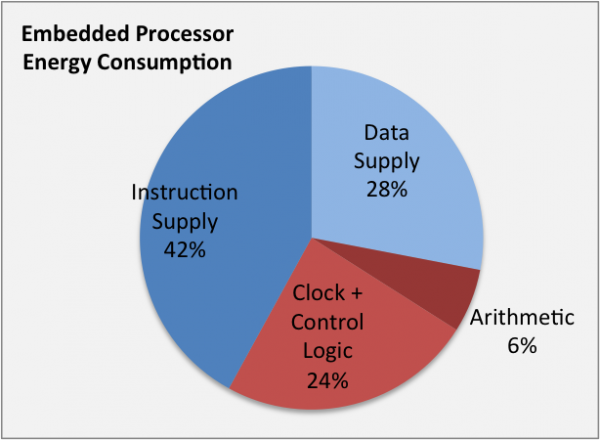

Another study by Dally et al published in IEEE Computer found that 42% of a typical embedded processor’s energy consumption comes from instruction fetching, and only 6% is consumed by performing the actual arithmetic operations.

Both these studies used a small, on-chip cache. When instructions more realistically need to be accessed from larger, on-chip or even worse off-chip memory, the impact is magnified, and the factor of 6.8x can go to 50x or more.

The conclusion here is clear: using an ISA that requires fewer instructions is a much bigger energy saver than simply selecting a processor that executes more efficiently.

Code Density’s Effect On Area

Area (gate usage) for a CPU is another common criterion for processor selection. But the area an SoC needs for program memory can be much larger, especially for non-dense code.

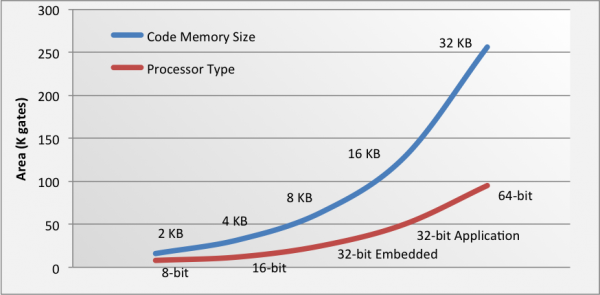

A general rule of thumb across technology nodes is that 1 kbit of on-chip SRAM occupies about the same space as 1K of logic gates. Applying this rule to some typical processors results in the area curves shown in Figure 2. (Here processor area estimates range from 8K gates for small 8-bit processors to 100K gates for sophisticated 64-bit processors, and on-chip code memory size estimates for suitable embedded programs range from 2 to 32 KBytes.)

This graph makes it clear that in most 32-bit embedded SoCs, program memory is two or more times larger than CPU area.

Denser code obviously needs smaller program memory. Selecting a processor that uses a denser ISA can therefore provide a significantly better impact on reducing SoC area over just considering the gate count needed for that CPU.

Code Density and the BA22 Family

The considerations above make the BA22 family of 32-bit processor cores we offer especially worthy of consideration for any processor-based system for which low power consumption is critical.

We believe the BA22 has the greatest code density in the industry, estimated up to 20% better than the impressive ARM® Thumb-2 ISA.

Competitive performance (2.1 or more Coremarks/MHz), area (from 15K gates), clock rates (more than 400 MHz on 65nm-LP), and power efficiency (0.02 mW/MHz), along with this superior code density make the BA22 one of the best possible CPU choices for deeply embedded systems where total power consumption really matters.

Give us an email or call any time (+1 201.391.8300) to learn discuss your project needs.