## SHA-384/512

### SHA-384 and SHA-512 Secure Hash Crypto Engine

#

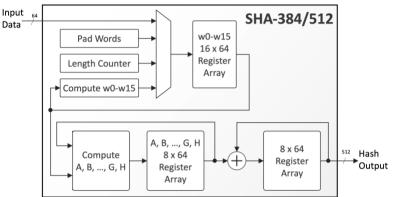

The SHA-384/512 is a high-throughput, and compact hardware implementation of the SHA-384 and the SHA-512 cryptographic hash functions provisioned by the FIPS180-4 standard.

The core is designed for ease of use and integration and adheres to industry-best coding and verification practices. Technology mapping, and timing closure are trouble-free, as the core contains no multi-cycle or false paths, and uses only rising-edge-triggered D-type flip-flops, no tri-states, and a single-clock/reset domain. The SHA-384/512 core features a simple input and output data interface. Support for AMBA bus interfaces and integration with an external DMA are available as options.

The highly reliable SHA-384/512 has been production-proven in several ASIC and FPGAs designs.

#### **Block Diagram**

#### **Applications**

The SHA-256 can be used in various applications for ensuring data integrity, and authenticity. Some examples are on-chip communication, electronic fund transfers, digital signatures, password storage, blockchain technology and data backup.

#### **Implementation Results**

The SHA-384/512 core can be mapped to any AMD FPGA device (provided sufficient silicon resources are available). The following are sample results with all core I/Os assumed to be routed on-chip.

| Technology              | Logic<br>Resources | Memory<br>Resources | Freq.<br>(MHz) | Throughput<br>(Mbps) |

|-------------------------|--------------------|---------------------|----------------|----------------------|

| Kintex UltraScale (-1)  | 2,132 LUT          | -                   | 275            | 3,477                |

| Kintex UltraScale+ (-1) | 1,974 LUT          | -                   | 350            | 4,425                |

| Virtex UltraScale+ (-2) | 2,304 LUT          | -                   | 475            | 6,005                |

| Versal (-2MP)           | 2,453 LUT          | -                   | 375            | 4,741                |

The provided figures <u>do not</u> represent the higher speed or smaller area for the core. Please contact CAST to get characterization data for your target configuration and technology.

#### **FEATURES**

- Custom-hardware accelerator for the SHA-384 and SHA-512 cryptographic hash functions

- Compliant to FIPS 180-4 with input message length up to (2<sup>128</sup> – 1) bits

- High throughput:

- 81 clock-cycles per 1024-bit input block

- Throughput scaling with multiple clock instances.

- Small silicon footprint: ~2,300 LUTs

- Easy integration & implementation

- Fully synchronous, uses only the rising clock-edge, singleclock domain, no false or multicycle timing paths, scanready, LINT-clean, reusable design

- Simple input and output interfaces, optionally bridged to AMBA™ interfaces or integrated with a DMA engine.

- Available in VHDL or Verilog source code format, or as a targeted FPGA

- Complete deliverables include test benches, C model, and test vector generator

- Multiple times production-proven in ASIC and FPGA designs

#### Support

The core as delivered is warranted against defects for ninety days from purchase. Thirty days of phone and email technical support are included, starting with the first interaction. Additional maintenance and support options are available.

#### Deliverables

The core is available in RTL (VHDL or Verilog) source code, or as a targeted FPGA netlist. Its deliverable package includes the following:

- Sophisticated self-checking HDL testbench

- C Model & test vector generator

- Sample simulation & synthesis scripts

- User documentation

#### **Export Permits**

This core implements encryption functions and as such it is subject to export control regulations. Export to your country may or may not require a special export license. Please contact CAST to determine what applies in your specific case.

www.cast-inc.com • info@cast-inc.com Contents subject to change without notice. Trademarks are the property of their respective owners. Engineered by