# **CSENT** SENT/SAE J2716 Controller

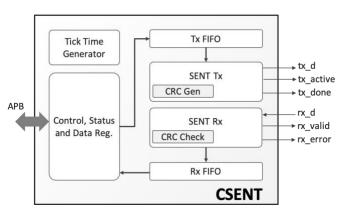

The CSENT core implements a controller for the Single Edge Nibble Transmission (SENT) protocol. It complies with the SAE J2716 standard and is capable of driving pulses to trigger synchronous Sensor type. It can be used for conveying data from one or multiple sensors to a centralized controller using a single SENT line.

The CSENT core can be configured as a Transmitter and/or as a Receiver, and therefore it suitable for adding a interface to devices transmitting sensor data or controllers receiving sensor data. It provides access to its control, status, and data registers 32-bit APB bus interface, comprehensive set of interrupt signals facilitates

interrupt-based operation. The core allows for Transmitter operation without requiring any external programming or control. The reset values for all its control registers are defined at synthesis time, and at run time the system only needs to write sensor data to the core.

The CSENT core is designed with industry best practices. The core contains no latches or tristates, and is fully synchronous with a single clock domain. The core is available in Verilog or as targeted FPGA netlist. Deliverables provide everything required for a successful implementation, including sample scripts, an extensive testbench, and comprehensive documentation.

## **Applications**

The CSENT core is suitable for designing low-cost digital automotive sensors and automotive controller units.

## Size and Performance

The following are sample Intel/Altera implementation results, which do not represent the the core and do not include the area for the implementation of the FIFOs.

| Configuration   | Target Technology          | Area               | Fmax    |

|-----------------|----------------------------|--------------------|---------|

| TX & RX no FIFO | StratixV / 5sgxea9n3fc5c4  | 570 ALMs, 693 Regs | 315 MHz |

| TX only no FIFO | StratixV / 5sgxea9n3fc5c4  | 275 ALMs, 351 Regs | 339 MHz |

| TX & RX no FIFO | CyloneV / 5ceba9f31c7      | 571 ALMs, 697 Regs | 162 MHz |

| TX only no FIFO | CyloneV / 5ceba9f31c7      | 279 ALMs, 351 Regs | 185 MHz |

| TX & RX no FIFO | ArriaV / 5agxbb3d4f35c4    | 570 ALMs, 701 Regs | 204 MHz |

| TX only no FIFO | Arria10 / 10as057k2f35i2lg | 280 ALMs, 352 Regs | 247 MHz |

| TX & RX no FIFO | US Kintex / xcku035-3      | 593 ALMs, 688 Regs | 365 MHz |

| TX only no FIFO | Arria10 / 10as057k2f35i2lg | 284 ALMs, 349 Regs | 401 MHz |

### **FEATURES**

#### SENT/SAE J2716 Receiver & Transmitter

- Fast and Slow Channel Transmit or Receive

- CRC generation for Transmitter, and CRC checking for Receiver

- All types of SENT Frames

- Programmable data length (4 to 24 bits) for Fast Channel Frames

- Short (8-bit data) and Enhanced (12or 16-bit data) Message Formats for Slow Channel

- Optional Pause Pulse with programmable length

- Supports inverted SENT protocol

#### **Trigger Pulse for Synchronous Sen**sors

- Allows up to four sensors (transmitters) to use the same physical SENT connection

- Programmable master trigger pulse length

#### Ease of Integration

- 32-bit APB interface, and comprehensive set of interrupts

- Programmable 4-bit clock divider and high precision 16-bit clock pre-scale

- Receive and Transmit FIFO of configurable size for Fast Channel data

- Run-time programmable configuration registers

- Synthesis-time defined reset values for all registers, enables data transmit without control from host processor

- LINT-clean, single-clock domain, scan-ready design

#### **Deliverables**

- Targeted netlist

- Testbench

- Sample synthesis and simulation scripts

- Documentation