Silicon IP Cores

BA21

32-bit Low-Power Deeply Embedded Processor

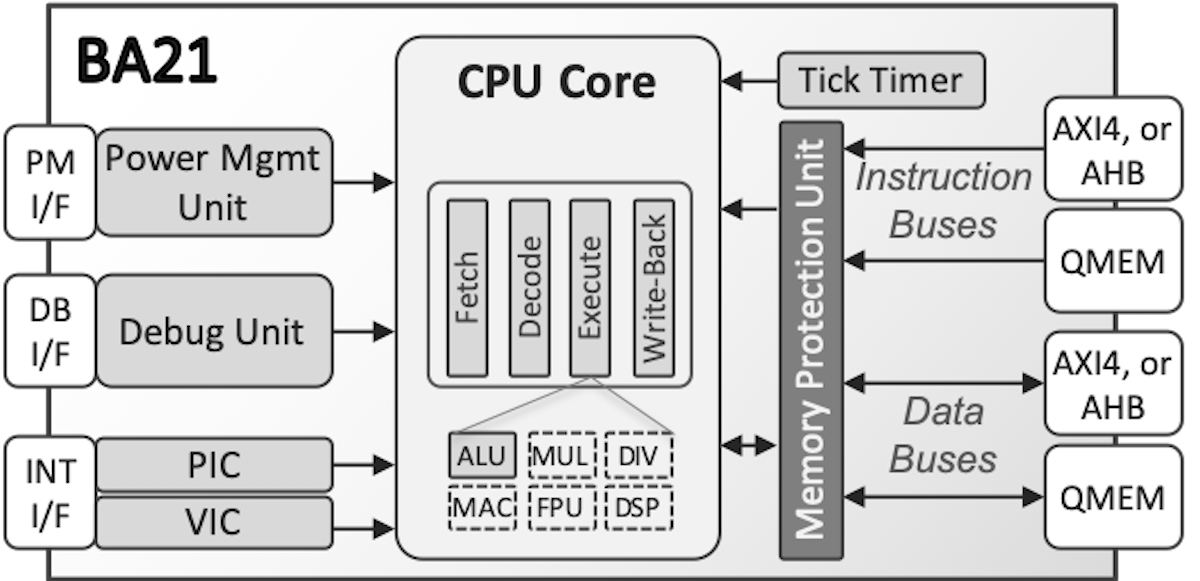

The BA21 is a royalty free 32-bit low-power processor that delivers better performance than most processors of its size. Designed for deeply-embedded systems or as an auxiliary processor in larger systems, it is an especially effective choice for analog modules management, calibration, and configuration in energy- and cost-sensitive applications.

The two-stage pipelined architecture minimizes standby/idle power and run-time energy consumption. The small silicon footprint of the CPU, and the smaller code memory requirement (due to the extreme code density of the BA2 instruction set), are critical for minimizing leakage currents during idle or standby modes and reducing dynamic power consumption. Furthermore, the processor allows for sophisticated power management, enabling dynamic clock gating or power shut off of unused modules, and software or hardware controller dynamic frequency scaling of the bus and the CPU.

Delivering more processing power per MHz than most processors in its class, the BA21 can be configured to operate at low frequencies to further save power, or to meet the most demanding embedded processing requirements, or any optimum combination of both. Its processing capabilities can be enhanced with the optional hardware multiplier, divider, multiply-accumulate, IEEE 754 compliant floating-point, and DSP instructions acceleration units. Interrupt response time can be optimized further with a vectored interrupt controller, and an optional memory protection unit can be used to protect application code and/or data from corruption. The system interface uses two AMBA® AXI4™ or optionally two AHB-Lite™ buses, one for data and one for instructions. Two tightly-coupled quick memory (QMEM) buses allow fast access for time-critical code and data and can be used for inter-core communication in a multi-core architecture.

The BA21 supports the variable instruction length BA2 instruction set, benefits from its extreme code density, and is binary compatible with other members of the BA2x processor family. Programing is facilitated with the included C/C++ tool chain, Beyond Studio IDE, architectural simulator, and ported C libraries.. Additional peripherals and bus infrastructure cores or complete subsystems can be ordered with the processor core to simplify SoC integration.

Part of the royalty-free BA2x family, the BA21 processor core has been designed for easy reuse and integration, has been rigorously verified, and is production proven.

The BA2 instruction set provides extreme code density without compromises on performance, ease of use, or scalability. It features:

- A linear, 32-bit address space

- Variable length instructions: 16, 24, 32, or 48 bits

- Simple memory addressing modes

- A configurable number of 12 to 32 general purpose registers

- Efficient flow-control, arithmetic, and load/store instructions

- Floating point and DSP extensions

The core is delivered with BeyondStudio™, a complete Integrated Development Environment (IDE) for Windows and Linux under Eclipse. BeyondStudio includes a highly featured source code editor, supports graphical source-level debugging and GUI based configuration, and can be extended with a collection of available or custom plug ins.

The IDE integrates an Instruction level simulator and a GNU cross-compiling toolchain. The GNU Compiler Collection (GCC), includes front ends for C, C++, Objective-C, Fortran, Java, and Ada; libraries for these languages (e.g. libstdc++, libgcj, etc) are provided. The tool chain also includes the GNU Binutils collection of binary tools, and the GNU Project Debugger (GDB).

Extensive support of libraries enables easy application development for Linux and Android. Finally, hardware targets can be interfaced with the cost effective Beyond Debug Key, which in addition to standard JTAG (IEEE 1149.1 and IEEE 1149.7) also supports proprietary One Wire Debug and Two Wire Debug protocols. The available Talos-BA2x Evaluation Kit for the BA21 includes the Debug Key, a reference design on an FPGA board, and drivers and other software.

Support and Services

The core as delivered is warranted against defects for 90 days from purchase. Thirty days of phone and email technical support are included, starting with the first interaction. Additional maintenance and support options are available.

IP Integration Services are also available to help minimize time to market for BA21-based systems. The processor core can be delivered pre-integrated with bus infrastructure cores, typical microcontroller peripherals, memory controllers, and interconnect IP cores. Contact CAST Sales for details.

Deliverables

The core is available for ASICs in synthesizable Verilog source code or for FPGAs in optimized netlists. It includes everything required for successful implementation: extensive documentation, a testbench, a sample SoC design, sample synthesis and simulation scripts, and the BeyondStudio™ Eclipse-based software development IDE for Windows and Linux.

Reference designs on FPGA boards are also available; contact CAST Sales for information.

Engineered by Beyond Semiconductor.

Features List

Low-Power 32-bit Processor

- Small silicon footprint for lower leakage and dynamic CPU power

- From 7300 sq. µm in 28nm, or approximately 10K gates

- BA2 ISA allows extreme code density for fewer instruction fetches and lower energy usage

- Advanced power management

- Dynamic clock gating and power shut off of unused units

- Software- and hardware-controlled clock frequency

- Wake up on tick timer or external interrupt

Processing Efficiency

- 2.77 Coremarks/MHz

- Up to 400 MHz in 28 nm

Optional Processor Units

- Programmable Vectored Interrupt Controller Unit

- Memory Protection Unit

- Timer Unit

- Debug Unit

- ROM Patching Unit

- Hardware Multiplier and/or Divider

- Multiply-Accumulate Unit

- Floating Point Unit

- DSP Instructions Acceleration Unit

Advanced Debug Capability

- Non-intrusive debug/trace for both CPU and system

- Complex chained watchpoint and breakpoint conditions

- Standard JTAG and proprietary Two-Wire Debug interface

Available Pre-Integrated Platforms

- Microcontroller peripherals such as GPIO, UART, Real-Time Clock, Timers, I2C, and SPI

- Memory controllers, interconnect IP, and more

Easy Software Development

- Beyond Studio IDE for Windows & Linux

- C /C++ compiler, debugger, linker, assembler, and utilities

- Architectural simulator

- Ported libraries and RTOS

Ready for Evaluation

- Talos-BA2x Evaluation Kit includes a debug key, FPGA board with reference design, drivers and software