Silicon IP Cores

SCR

Smart Card Reader Controller

Implements an interface and controller for communicating between smart cards and host systems using a variety of standard system interfaces.

The SCR supports the ISO/IEC 7816-3:2006 and EMV 4.3 specifications, which define the electrical signals and transmission protocols for smart cards (also known as integrated circuit cards). It acts as a communication controller, passing data to and from the host system and the smart card. It is fully-featured, and can activate and deactivate cards, perform cold/warm resets, handle ATR response reception, and execute other essential functions.

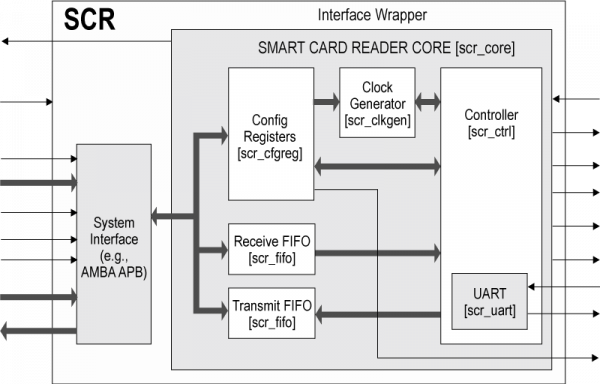

The SCR consists of the core smart card reader logic with a wrapper for the desired system interface. (AMBA APB interface is available; support for AMBA AXI4-Lite, Avalon-MM or Wishbone is optional.)

The core is fully synchronous for easier testing and is designed for efficient ASIC or FPGA implementation. It requires, for example, just 6,500 ASIC gates and operates at 300 MHz (TSMC 0.13). This smart card reader core has been rigorously verified and multiple times production-proven.

The SCR manages the interactions between an inserted smart card and the host system. It handles all timing issues, and safely transfers data from and to the card.

As shown in the block diagram, the core consists of a main SCR core block which performs according to the 7816 specification, and a wrapper that interfaces the SCR functions to a host system with APB.

SCR Top Level Entity

The wrapper that connects the SCR core to the AMBA APB. It converts the APB signals and makes them useful to the core.

Smart Card Reader Core

Contains five blocks that implement the SCR, and communicates with the host system through the APB wrapper.

Configuration Registers

Store values that provide control over all SCR functions.

Controller with UART

The main functional block, controlling the received and transmitted characters and performing card activation and deactivation, and cold and warm reset.

Includes a UART (Universal Asynchronous Receiver Trans-mitter) that converts the data from parallel to serial for transmitting from the SCR to a Smart Card and from serial to parallel for transmitting from a Smart Card to the SCR. The UART also performs the guard time, parity checking, and character repeating functions.

Receive FIFO

Stores the data received from the smart card until it is read out by the host system.

Transmit FIFO

Stores the data to be transmitted to the smart card.

Clock Generator

Generates the Smart Card Clock and the Baud Clock Im-pulse signals, used in timing the SCR.

The core has been verified through extensive simulation, synthesis, and rigorous code coverage measurements. It has been embedded in numerous shipping customer products, and is proven in both ASIC and FPGA technologies

Support

The core as delivered is warranted against defects for ninety days from purchase. Thirty days of phone and email technical support are included, starting with the first interaction. Additional maintenance and support options are available.

Deliverables

The core includes everything required for successful implementation:

- HDL RTL source code or FPGA netlist

- Sophisticated, self-checking HDL Testbench including everything necessary to test the core

- Sample driver in C code

- Scripts for simulation and synthesis

- Comprehensive user documentation, including detailed specifications and design integration guidelines

The SCR can be mapped to any ASIC technology or FPGA device (provided sufficient silicon resources are available). The following table provides sample results for the APB version. Please contact CAST to get characterization data for your target configuration and technology.

| ASIC Technology | Cell Area (µm2) |

Gate Count |

Freq. (MHz) |

|---|---|---|---|

| TSMC 180nm process | 80,764 | 8,093 | 260 |

| TSMC 130nm process | 37,921 | 7,447 | 423 |

| TSMC 90nm process | 19,703 | 6,980 | 775 |

| TSMC 65nm process | 12,878 | 8,049 | 1040 |

The SCR can be mapped to any ASIC technology or FPGA device (provided sufficient silicon resources are available). The following table provides sample results for the APB version, optimized for area and using two 32x8 FIFOs. Please contact CAST to get characterization data for your target configuration and technology.

| Intel Devices | Logic Resources |

Memory Resources |

I/Os | Fmax (MHz) |

|---|---|---|---|---|

| Max® 10 10M08SCE144C8G |

1,080 LEs | 2 RAM Blocks | 10 | 127 |

| Cyclone® 10 LP 10CL006YU256C8G |

1,073 ALMs | 2 RAM Blocks | 10 | 134 |

| Arria® 10 10AS016C4U19I3SG |

552 ALMs | 2 RAM Blocks | 10 | 341 |

The SCR can be mapped to any ASIC technology or FPGA device (provided sufficient silicon resources are available). The following table provides sample results for the APB version, optimized for area and using a 2 x 8 byte FIFO. Please contact CAST to get characterization data for your target configuration and technology.

| AMD Devices | Area | BRAM | Fmax (MHz) |

|---|---|---|---|

| Spartan-6 6SLX25-2 |

246 Slices | - | 84 |

| Virtex-4 4VLX25-10 |

436 Slices | - | 165 |

| Virtex-5 5VLX30-1 |

192 Slices | - | 144 |

| Virtex-6 6VLX75T-1 |

172 Slices | - | 180 |

| Artix-7 7A15T-1 |

240 Slices 650 LUts |

- | 161 |

| Kintex-7 7K70T-1 |

220 Slices 657 LUTs |

- | 271 |

|

Kintex UltraScale KU025-1 |

131 CLBs 674 LUTs |

- | 339 |

|

Kintex UltraScale+ |

119 CLBs |

- | 488 |

The SCR can be mapped to any ASIC technology or FPGA device (provided sufficient silicon resources are available). The following table provides sample results for the APB version, optimized for area and using a 2 x 8 byte FIFO. Please contact CAST to get characterization data for your target configuration and technology.

| Lattice Devices | LUT-4s | Registers | PFUs | SysMEM EBRs |

External I/Os | Speed (Fmax, MHz) |

|---|---|---|---|---|---|---|

| ispXPGA LFX200C-4 |

705 | 427 | 248 | – | 54 | 60 |

| ORCA-4E OR4E02-3 |

757 | 396 | 131 | – | 54 | 71 |

The SCR can be mapped to any ASIC technology or FPGA device (provided sufficient silicon resources are available). The following table provides sample Microsemi results for the APB version, optimized for area and using a 2 x 16 byte FIFO. Please contact CAST to get characterization data for your target configuration and technology.

| Microchip Devices | Cells | Ram Blocks |

I/Os | Fmax (MHz) |

|

|---|---|---|---|---|---|

| Sequ (R) | Comb (C) | ||||

| Axcelerator AX125-3 |

412 | 1030 | 2 | 54 | 47 |

| ProASIC A500K050-STD |

413 | 1679 | 2 | 54 | 38 |

The SCR core is available in two versions: Standard and Safety-Enhanced. The Safety-Enhanced version implements spatial redundancy for protecting the inner logic of the core. The Safety-Enhanced version is certified as ISO-26262 ASIL-B Ready.

Features List

- Supports the ISO/IEC 7816-3:2006 and EMV 4.3 specifications

- Performs functions needed for complete smart card sessions, including:

- Card activation and deactivation

- Cold/warm reset

- Answer to Reset (ATR) response reception

- Data transfers to and from the card

- Extensive interrupt support system

- Adjustable clock rate and bit (baud) rate

- Configurable automatic byte repetition

- Handles commonly used communication protocols:

- T=0 for asynchronous half-duplex character transmission, and

- T=1 for asynchronous half-duplex block transmission

- Automatic convention detection

- Automatic voltage class selection

- Adjustable FIFOs for Receive and Transmit buffers (up to 32k characters) with threshold

- Configurable timing functions:

- Smart card activation time

- Smart card reset time

- Guard time

- Timeout timers

- Supports synchronous and any other non-ISO 7816 and non-EMV’96 or EMV2000 cards

- Standard system interface wrapper architecture for easy integration with host systems

- Fully-synchronous design suitable for scan-based testing

- Available in synthesizable HDL source code (versions for FPGAs also available)

Safety Enhanced Version (Optional)

- ISO 26262 ASIL-B Ready

- Implements spatial redundancy for inner logic protection

Resources

- Smart Card Basics by Cardlogix

- Smart Card Tutorial by Dr. David B Everett

- Info and links to numerous additional resources in the alt.technology.smartcards FAQ

- Purchase the ISO/IEC 7816-3:2006 standard