Silicon IP Cores

CAN-CTRL

CAN CC, CAN FD, and CAN XL Bus Controller

The CAN-CTRL implements a highly featured and reliable CAN bus controller that performs serial communication according to the Controller Area Network (CAN) protocol. It supports classical CAN, CAN FD & CAN XL according to ISO 11898-1:2024; Time-Triggered CAN (TTCAN) per ISO 11898-4; and CAN Frame time-stamping as described in the CiA 603 profile. This CAN controller core handles data rates exceeding 20Mbit/s and it is optimized for the AUTOSAR and SAE J1939 specifications.

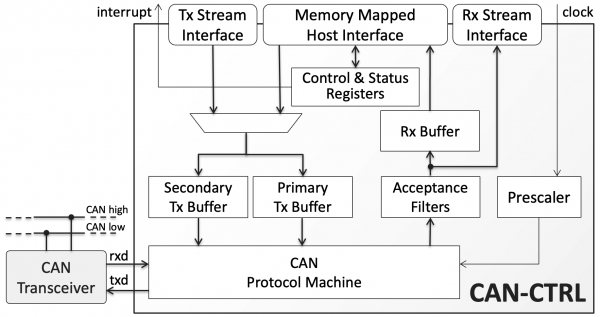

The CAN-CTRL is especially efficient in minimizing host CPU overhead and simplifying software development. It automatically drops incoming messages using run-time programmable acceptance filters, so that unwanted messages never reach the host system. The core also enables flexible scheduling of outgoing messages with minimum software overhead. To this end, the core implements two transmit buffers: the primary transmit buffer (PTB) and the secondary transmit buffer (STB). The PTB is able to store one CAN frame while the number of stored frames inside the STB is configurable. The STB may operate either in FIFO mode or may do frame reordering based on the priority of the CAN frame ID. The PTB has always highest priority regardless of the frame ID. Furthermore, polling the status of the core is not necessary because an interrupt line—driven by runtime maskable sources—notifies the host about actionable events on the CAN data bus or in the CAN controller core.

Designed for ease of integration, the CAN-CTRL is controlled by and exchanges data with the host system via a single memory-mapped slave interface. This memory-mapped interface can be either a generic 32-bit or 8-bit parallel interface, or optionally a 32-bit AMBA® APB, AHB-Lite, Wishbone, or Avalon-MM interface. Data can optionally be transferred to and from the core via dedicated 32-bit Avalon ST streaming interfaces. Using these dedicated streaming interfaces might be preferable in cases where messages are transferred to and from the system memory by an external DMA engine or when tight integration with a CANsec or other custom-hardware engine is required. To avoid limiting the host system, the host interfaces operate in an independent clock domain, which can be either synchronous or asynchronous to the core clock. Finally, to ease network operation, the core implements functionality similar to the Philips SJA1000 working with its PeliCAN mode extensions, providing error detection and analysis, bus diagnostics and optimization features

Proven in hundreds of shipping products, certified by reputable testing houses, verified with third-party VIP, conformance-tested in plugfests, and developed to CAST’s stringent quality standards, the CAN-CTRL is likely the most reliable CAN controller IP core available.

The CAN bus controller comes in three variants: CC, FD, and XL. The CC variant supports only Classical CAN, the FD vari-ant adds support for CAN FD, and the XL variant supports the Classical CAN, CAN FD, and CAN XL standards.

Each of the three core variants is available in two versions: Standard, and Safety-Enhanced. The Safety-Enhanced version implements ECC for SRAMs protection and uses spatial redundancy for protecting the inner logic of the core. The Safety-Enhanced versions are certified as ISO-26262 ASIL-D Ready.

Verification

The core has been rigorously verified and has been production-proven multiple times.

It has been verified through extensive synthesis, place and route, simulation runs, Verification IP, and PlugFests. It has been embedded in several shipping customer products and is proven in both ASIC and FPGA technologies. Several customer products have been certified for compliance by independent testing houses.

Support

The core as delivered is warranted against defects for ninety days from purchase. Thirty days of phone and email technical support are included, starting with the first interaction. Additional maintenance and support options are available.

The core will be modified if needed, to remain compatible with future versions of ISO 11898-1:2024 standard, CiA’s specification and with future updates of the related ISO 11898-1 standard. Customers shall receive updates for as long as they remain under support and maintenance coverage.

Deliverables

The core includes everything required for successful implementation:

- VHDL or Verilog RTL source code

- Post-synthesis netlist

- Testbenches

- Behavioral tests

- Post-synthesis verification

- Simulation scripts

- Synthesis scripts

- Low-Level Hardware Abstraction Layer (HAL) and Linux driver

- Optional MISRA C non-OS, bare-metal driver with advanced software examples

- Documentation and RUVM register descriptions.

- The optional safety-enhanced package includes the Safety Manual (SAM), a Failure Modes, Effects and Diagnostics Analysis (FMEDA) and the ASIL-D Ready certificate, issued by SGS-TÜV Saar GmbH.

The CAN-CTRL can be mapped to any ASIC technology or FPGA device (provided sufficient silicon resources are available). The following are sample results for the core configured with three receive buffers, three transmit buffers, and three acceptance filters (does not include priority mode, TTCAN and CiA603 timestamping).

| Configuration | Technology | Cell Area (eq. Gates) |

Memory Bits |

|---|---|---|---|

| CAN CC | TSMC 28nm HPC | 9,000 | 2,688 |

| CAN FD | TSMC 28nm HPC | 11,000 | 6,272 |

| CAN XL | TSMC 28nm HPC | 15,000 | 133,248 |

| CAN CC – Safe | TSMC 28nm HPC | 30,000 | 3,864 |

| CAN FD – Safe | TSMC 28nm HPC | 35,000 | 9,212 |

| CAN XL – Safe | TSMC 28nm HPC | 45,000 | 216,528 |

Please contact CAST to get characterization data for your target configuration and technology.

The CAN-CTRL can be mapped to any Altera FPGA device (provided sufficient silicon resources are available). The following are sample results for the core configured with three receive buffers, three transmit buffers, and three acceptance filters (does not include priority mode, TTCAN and CiA603 timestamping).

| Family Device | CAN CC | CAN-FD | ||

|---|---|---|---|---|

| Logic | Memory | Logic | Memory | |

| Max 10 10M50 |

2,343 LEs 0 MULTs |

1,088 bits 3 RAM Blocks |

2,806 LEs 0 MULTs |

4,224 bits 3 RAM Blocks |

| Cyclone V 5CEFA7 |

1,094 ALMs 1 DSP |

1,325 ALMs 1 DSP |

||

| Cyclone 10 LP 10CL120 |

2,331 LEs 0 MULTs |

2,808 LEs 0 MULTs |

||

| Cyclone 10 GX 10AX115 |

1,072 ALMs 1 DSP |

1,317 ALMs 1 DSP |

||

| Arria V GX 5AGXBB3 |

1,092 ALMs 1 DSP |

1,217 ALMs 1 DSP |

||

| Arria 10 GX 10AX115 |

1,117 ALMs 1 DSP |

1,333 ALMs 1 DSP |

||

Note: Host and CAN clock constrained to 80MHz

When CAN XL support is added, the CAN-CTRL core occupies approximately 1,750 ALMs and requires 133k of memory bits.

Please contact CAST to get characterization data for your target configuration and technology.

The CAN-CTRL can be mapped to any AMD FPGA device (provided sufficient silicon resources are available). The following are sample results for the core configured with three receive buffers, three transmit buffers, and three acceptance filters (does not include priority mode, TTCAN, and CiA603 timestamping).

| Configuration | Device Family | |||

|---|---|---|---|---|

| Artix 7 | Virtex 7 | Kintex US | Kintex US+ | |

| CAN CC | 1,847 LUTs 1 BRAM Tile |

1,855 LUTs 1 BRAM Tile |

1,822 LUTs 1 BRAM Tile |

1,823 LUTs 1 BRAM Tile |

| CAN CC – Safe | 6,993 LUTs 1.5 BRAM Tile |

6,979 LUTs 1.5 BRAM Tile |

6,924 LUTs 1.5 BRAM Tile |

6,925 LUTs 1.5 BRAM Tile |

| CAN FD | 2,270 LUTs 1 BRAM Tile |

2,266 LUTs 1 BRAM Tile |

2,250 LUTs 1 BRAM Tile |

2,244 LUTs 1 BRAM Tile |

| CAN FD – Safe | 8,353 LUTs 1.5 BRAM Tile |

8,291 LUTs 1.5 BRAM Tile |

8,347 LUTs 1.5 BRAM Tile |

8,327 LUTs 1.5 BRAM Tile |

| CAN XL | 3,423 LUTs 8 BRAM Tile |

3,417 LUTs 8 BRAM Tile |

3,465 LUTs 8 BRAM Tile |

3,467 LUTs 8 BRAM Tile |

| CAN XL – Safe | 12,071 LUTs 13 BRAM Tile |

12,012 LUTs 13 BRAM Tile |

11,767 LUTs 13 BRAM Tile |

11,747 LUTs 13 BRAM Tile |

Please contact CAST to get characterization data for your target configuration and technology.

The CAN-CTRL can be mapped to any Efinix FPGA device (provided sufficient silicon resources are available). The following are sample results for the core configured to support CAN CC and CAN-FD with three receive buffers, three transmit buffers, and three acceptance filters (does not include priority mode, TTCAN and CiA603 timestamping). The list of supported Efinix devices is not exhaustive.

| Family | Logic Resources |

Memory Resources |

Freq. (MHz) |

|---|---|---|---|

| Trion T8-Q144I4 |

3,802 LEs 1 Mult |

4 Mblock | 60 |

Please contact CAST to get characterization data for your target configuration and technology.

The CAN-CTRL can be mapped to any Lattice FPGA Device (provided sufficient silicon resources are available) and optimized to suit the particular project’s requirements. The following are sample results for the core configured with three receive buffers, three transmit buffers, three acceptance filters, and no support for TTCAN.

| Family | Variant | Logic Resources |

Memory Resources |

Host Clock (MHz) |

|---|---|---|---|---|

| Certus-NX LFD2NX-40 |

CAN XL | 4,276 Slices 4,043 LUT4 |

1 LRAM | 80 |

| Certus-NX LFD2NX-40 |

CAN FD | 4,238 Slices 3,876 LUT4 |

2 EBR | 69 |

| Certus-NX LFD2NX-40 |

CAN CC | 3,375 Slices 3,082 LUT4 |

2 EBR | 68 |

| ECP5 LFE5U-85F |

CAN FD | 1,810 Slices 2,752 LUT4 |

2 EBR | 80 |

| ECP5 LFE5U-85F |

CAN CC | 1,444 Slices 2,135 LUT4 |

2 EBR | 80 |

| ICE 40U/P5k |

CAN FD | 3,883 LCs 544 PLBs |

6 EBR | 42 |

| ICE 40U/P5k |

CAN CC | 2,932 LCs 452 PLBs |

6 EBR | 45 |

| MachXO2 7000HC |

CAN FD | 1,530 Slices 3,025 LUT4 |

6 EBR | 59 |

| MachXO2 7000HC |

CAN CC | 1,248 Slices 2,466 LUT4 |

6 EBR | 62 |

The CAN-CTRL can be mapped to any Microchip FPGA Device (provided sufficient silicon resources are available) and optimized to suit the particular project’s requirements. The following are sample results for the core configured with three receive buffers, three transmit buffers, three acceptance filters, and no support for TTCAN.

| Family | Variant | Logic Resources |

Memory Resources |

Freq. (MHz) |

|---|---|---|---|---|

| Igloo2 M2GL150-STD |

CAN CC | 2,774 4LUT | 2 RAM1K18 | 60 |

| Igloo2 M2GL150-STD |

CAN FD | 3,330 4LUT | 2 RAM1K18 | 60 |

| PolarFire MPF500T-STD |

CAN CC | 2,759 4LUT | 2 LSRAM | 100 |

| PolarFire MPF500T-STD |

CAN FD | 3,375 4LUT | 2 LSRAM | 100 |

| RTG4 RT4G150-STD |

CAN CC | 2,711 4LUT | 2 RAM1K18 | 60 |

| RTG4 RT4G150-STD |

CAN FD | 3,416 4LUT | 2 RAM1K18 | 60 |

| SmartFusion2 M2S150-STD |

CAN CC | 2,774 4LUT | 2 RAM1K18 | 60 |

| SmartFusion2 M2S150-STD |

CAN FD | 3,330 4LUT | 2 RAM1K18 | 60 |

Engineered by Fraunhofer IPMS.

Features List

CAN Specifications Support

- Classical CAN, CAN FD & CAN-XL (ISO 11898-1: 2024, & legacy versions)

- TTCAN (ISO 11898-4 level 1)

- CAN frame time-stamping (CiA 603)

- Optimized for AUTOSAR and SAE J1939

Enhanced Functionality

- Error Analysis features enabling diagnostics, system maintenance, and system optimization:

- Last error type

- Arbitration lost position

- Error Warning Limit

- Listen-Only Mode enables CAN bus traffic analysis and automatic bit-rate detection

- Loopback mode for self-testing

Flexible Message Buffering and Filtering

- Configurable number of:

- Receive and transmit buffers

- Independently programmable acceptance filters

- FIFO or priority mode for transmit frames, and high-priority transmit buffer for urgent traffic

Easy to Use and Integrate

- Programmable data rate. The data rate is practically limited by the transceiver and/or the bus configuration.

- Programmable baud rate prescaler

- Single Shot Transmission Mode for lower software overhead and fast reloading of transmit buffer

- Programmable interrupt sources

- Data access via a memory-mapped interface or via dedicated streaming interfaces

- Generic 32-bit or 8-bit and optional 32-bit AMBA-APB, 32-bit AHB-Lite, 32-bit Wishbone, or 32-bit Avalon-MM memory-mapped interface

- Compatible with any ISO 11898-2 and CAN SIC (CiA 601-4) transceiver

Safety Enhanced Version (optional)

- Certified as ISO-26262 ASIL-D Ready

- Implements ECC for SRAM and spatial redundancy for inner logic protection

Highly Reliable

- Proven in hundreds of automotive, aerospace, and industrial products

- Certified by testing houses, as part of customer products

- Robustly verified using extensive internal test suite, and 3rd party VIPs

- Plugfest-tested

Efficient and Portable Design

- Available in RTL, and portable to ASIC and FPGA technologies

Resources

Resources

- CAN Bit Time Calculator

- CAN in Automation (CiA) Knowledge Pages

- CiA CAN-XL SiG Page

- CAN entry at Wikipedia

- CAN FD entry in Wikipedia

- NMEA 2000 entry at Wikipedia

- DeviceNet entry at Wikipedia

- CANaerospace standard documents

- CANaeropsace entry in Wikipedia

- CAN Wiki

- The CANbus USA website of the ESAcademy

- SAE J1939 Standards collection

- AUTOSAR official web site

- Vector Informatik's CAN Pages

Articles

- "CAN FD: Anything But Automotive Only" By Bernd Westhoff at EE|Times

- Concise CAN XL description at CAN in Automation

- CANsec article by Tobias Belitz at Renesas