Silicon IP Cores

JPEG-E-S

Baseline JPEG Encoder

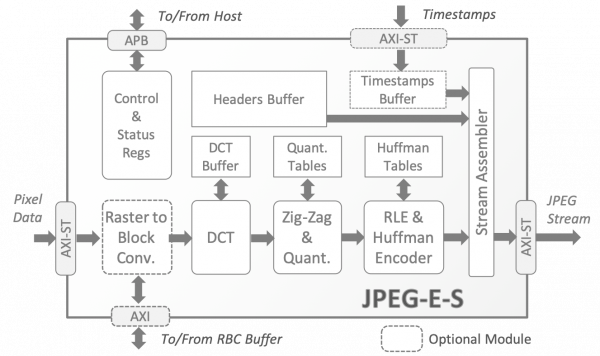

This JPEG compression IP core supports the Baseline Sequential DCT modes of the ISO/IEC 10918-1 standard. It implements an area-efficient, high-performance, hardware JPEG encoder with remarkably low processing latency.

The JPEG-E-S encoder produces compressed JPEG images and the video payload for Motion-JPEG container formats. It accepts images with 8-bit color samples and up to four color components, in all widely-used color subsampling formats.

The compact encoder processes one color sample per clock cycle, enabling it to compress multiple Full-HD channels even in low-cost FPGAs.

Once programmed, the easy-to-use encoder requires no assistance from a host processor to compress an arbitrary number of frames. SoC integration is straightforward thanks to standardized AMBA® interfaces: AXI Streaming for pixel and compressed data, and a 32-bit APB slave interface for registers access. Users can optionally insert timestamps or other metadata in the compressed stream using a dedicated AXI Streaming interface.

Customers with a short time to market priority can use CAST’s IP Integration Services to receive complete JPEG subsystems. These integrate the JPEG encoder with video interface controllers, Hardware UDPIP or Transport Stream networking stacks, or other IP cores available from CAST.

The core is designed with industry best practices, and its reliability and low risk have been proven through both rigorous verification and customer production. Its deliverables include a complete verification environment and a bit-accurate software model.

The core has been verified through extensive synthesis, place and route, and simulation runs. It has been embedded in several shipping customer products, and is proven in both ASIC and FPGA technologies.

Support

The core as delivered is warranted against defects for ninety days from purchase. Thirty days of phone and email technical support are included, starting with the first interaction. Additional maintenance and support options are available.

Deliverables

The core is available as a targeted FPGA netlist, and includes everything required for successful implementation. The deliverable package includes:

- Targeted netlist

- Sophisticated self-checking Testbench

- Software (C++) Bit-Accurate Model

- Sample simulation scripts

- Comprehensive user documentation

The JPEG-E-S core can be mapped to any Altera FPGA Device (provided sufficient silicon resources are available) and optimized to suit specific project requirements. The following table provides sample implementation and performance data for the default configuration of the core.

| 1080p30 4:2:2 |

720p60 4:4:4 |

1080p60 4:2:2 |

Logic Resources |

DSP | Memory Bits |

|

|---|---|---|---|---|---|---|

| Max10 | 9,300 LEs | 8 | 48,540 | |||

| CycloneV | 3,443 ALMs | 4 | 40,082 | |||

| Arria10 | 3,443 ALMs | 4 | 40,082 |

The JPEG-E-S core can be mapped to any AMD Device (provided sufficient silicon resources are available) and optimized to suit specific project requirements. The following table provides sample implementation and performance data for the default configuration of the core.

| 1080p30 4:4:4 |

1080p60 4:2:0 |

1080p60 4:2:2 |

LUTs | DSP | BRAMs | |

|---|---|---|---|---|---|---|

| Artix-7 (speed grade -2) |

5,030 | 4 | 2.5 | |||

| Kintex7 (speed grade -2) |

5,217 | 4 | 2.5 | |||

| Kintex7-US (speed grade -1) |

5,076 | 4 | 2.5 |

Note that the list of video formats is not exhaustive, and that these sample implementation figures do not represent the highest speed or smallest area possible for the core. Please contact CAST to discuss silicon resource utilization and performance for your target technology.

The JPEG-E-S core can be mapped to any Lattice Device (provided sufficient silicon resources are available) and optimized to suit specific project requirements. The following table provides sample implementation and performance data for the default configuration of the core.

| 1080p30 4:2:2 |

720p60 4:4:4 |

1080p60 4:2:2 |

Logic Resources |

Memory Resources |

|

|---|---|---|---|---|---|

| CrossLink-NX (-8HP) | 6,692 LUT4 4 MULT18 |

6 EBR |

The JPEG-E-S core can be mapped to any Microchip Device (provided sufficient silicon resources are available) and optimized to suit specific project requirements. The following table provides sample implementation and performance data for the core configured to support fixed Huffman tables and no rate control.

| Family / Device | Logic Resources |

Memory Resources / Device |

Freq (MHz) / Device |

|---|---|---|---|

| IGLOO2 / M2GL150-STD | 8,711 4LUTs | 26 RAM64x18 2 RAM1Kx18 |

140 |

| PolarFire / MPF500T-STD | 7,783 4LUTs | 32 uSRAM 7 LSRAM |

150 |

| RTG4 / RT4G150-STD | 8,563 4LUTs | 26 RAM64x18 2 RAM1Kx18 |

80 |

| SmartFusion2 / M2S150-STD | 8,711 4LUTs | 26 RAM64x18 2 RAM1Kx18 |

140 |

Note that the above implementation figures do not represent the highest speed or smallest area possible for the core. Please contact CAST to discuss silicon resource utilization and performance for your target technology and core configuration.

Engineered by Beyond Semiconductor.

Features List

Performs Baseline Sequential DCT JPEG encoding of images or video with small silicon area, high performance, and low latency.

Standards Support

- ISO/IEC 10918-1 Standard Baseline Sequential DCT mode

- Encodes single-frame JPEG images and Motion JPEG payloads

- 8-bit per color samples

- Up to four color components; any image size up to 64k x 64k

- Handles all scan configurations and all JPEG formats

- APP, COM, and restart markers

- Programmable Huffman and Quantization tables

Rate Control Options

- Image: Limits the size of each individual frame

- Video: Regulates bit rate over a number of input frames

Interfaces

- AXI Streaming I/O data interfaces

- APB Control/Status interface

- Optional AHB wrapper with DMA capabilities

Performance and Size

- One encoded sample per clock cycle

- Small silicon footprint (about 70k gates)

Ease of Integration

- Automatic program-once/encode-many operation

- Simple, dedicated timestamps interface

- Included bit-accurate software model generates test vectors, expected results, and core programming values

- Optional Raster-to-Block Conversion with AXI or standard memory interface to the lines buffer

Format

- Available as a targeted FPGA netlist

Resources

See the JPEG entry at Wikipedia.

See the Motion JPEG entry at Wikipedia.